Low Frequency Receiver (LFR)¶

Alexis Jeandet <alexis.jeandet@lpp.polytechnique.fr>:

Github:jeandet |

Gitter:jeandet |

IRC@freenode:jeandet

Laboratory of Plasma Physics (LPP)¶

Laboratory of Plasma Physics (LPP)¶

- Since 2009, fusion between LPTP and CETP

- Around 110+ people

- 3 Scientific teams, [Fusion, Cold, Space] Plasmas

Laboratory of Plasma Physics (LPP)¶

Plasmas are used in many daily applications, TVs, lights, energy production, air cleaning, IC manufacturing...

On the cosmic scale, 99 % of observed matter is ionized and therefore in the plasma state.

Laboratory of Plasma Physics (LPP)¶

- Natural Plasmas are mostly in space and need in-situ measurements such as:

- particles (particles detectors, spectrometers)

- E-field (Electric antenna)

- B-field (Search-coils, Flux-gates)

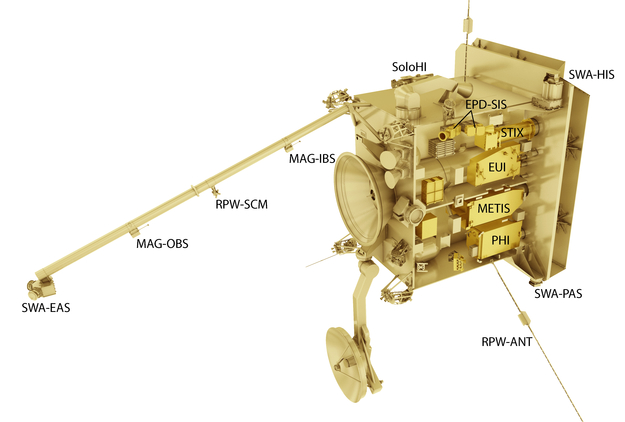

Solar Orbiter¶

- Sun observatory and Solar wind in-situ measurements

- Launch date: end of 2020

- Orbit 0.3 -> 0.8 AU

- Mass total/payload: 1800kg/190kg

- Power 1100W

- Data downlink ~150 kbps

Solar Orbiter¶

Small amount of telemetry implies heavy onboard computation.

Radio Plasma Waves instrument (RPW)¶

- Focuses on waves( E field & B field ) measurements from ~0Hz to 16MHz

- Composed of BIAS, TNR-HFR, TDS, DPU, LVPS-PDU, SCM, LFR

- ~10kb/s average telemetry

- ~5.5kg

- ~13W

Radio Plasma Waves instrument (RPW)¶

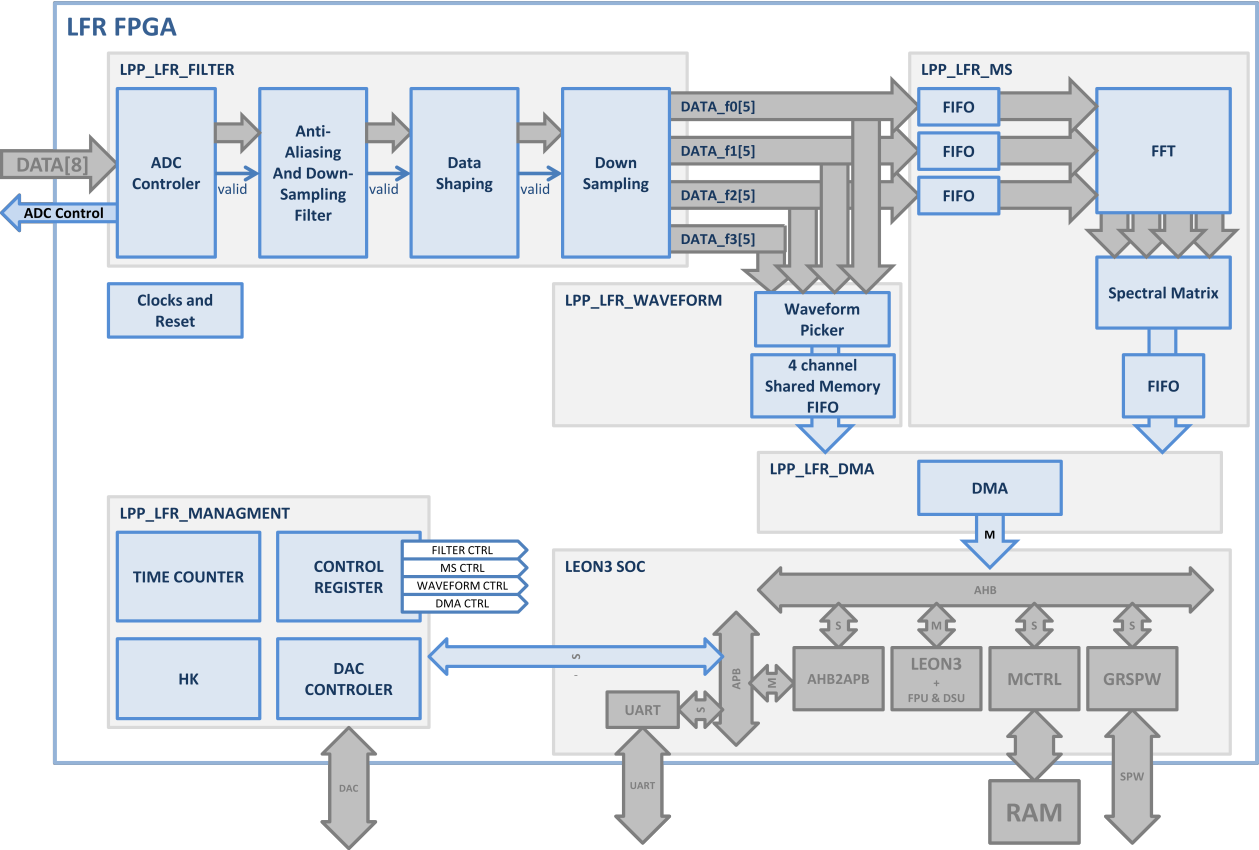

Low Frequency Receiver (LFR)¶

- Produces waveforms at 24576Hz, 4096Hz, 256Hz and 16Hz (F[0,1,2,3])

- Computes 256 points FFTs on F0 to F2 continuously (5 components 2E and 3B)

- Computes and averages Spectral Matrices continuously (5x5 matrix)

- Extracts high level Plasma quantities such as normal wave vector, wave ellipticity estimator, wave degree of polarization, z-component of the normalized Poynting vector, phase velocity estimator,...

- Provides continuous waveforms up to 4096S/s on demand (Burst modes)

Low Frequency Receiver (LFR)¶

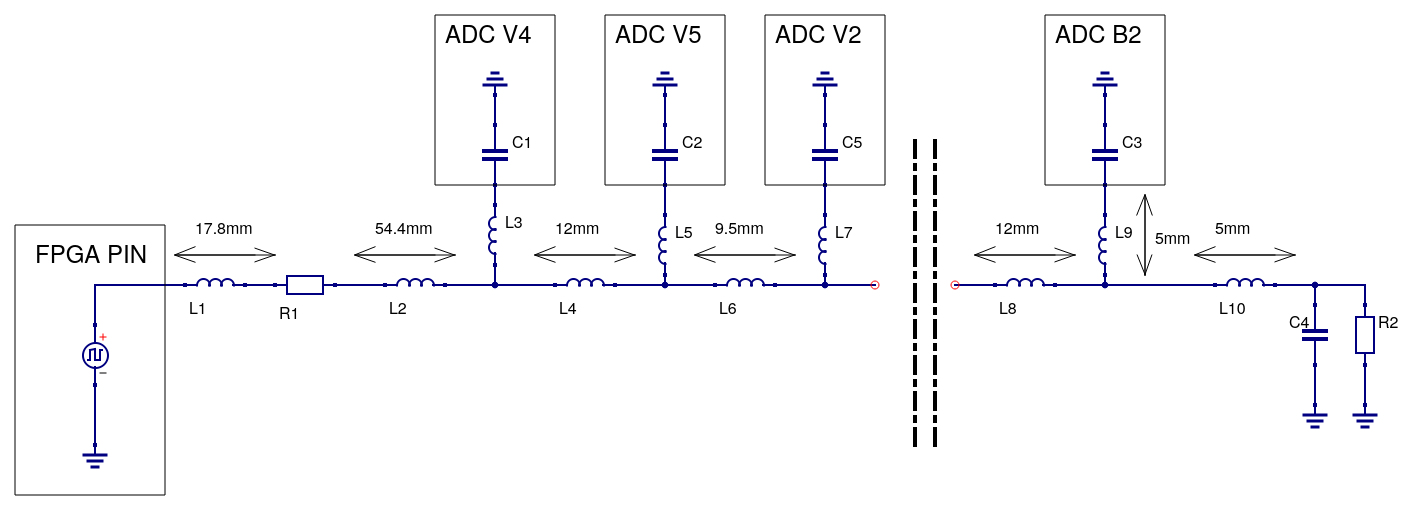

- 5 E-field and 3 B-field waves from ~0Hz to 10kHz -> 8 inputs

- less than 2W

- ~3-4kb/s average telemetry

- 240x160mm form factor

- Radiation hardened and fault tolerant

- -30°C : +75°C temperature range

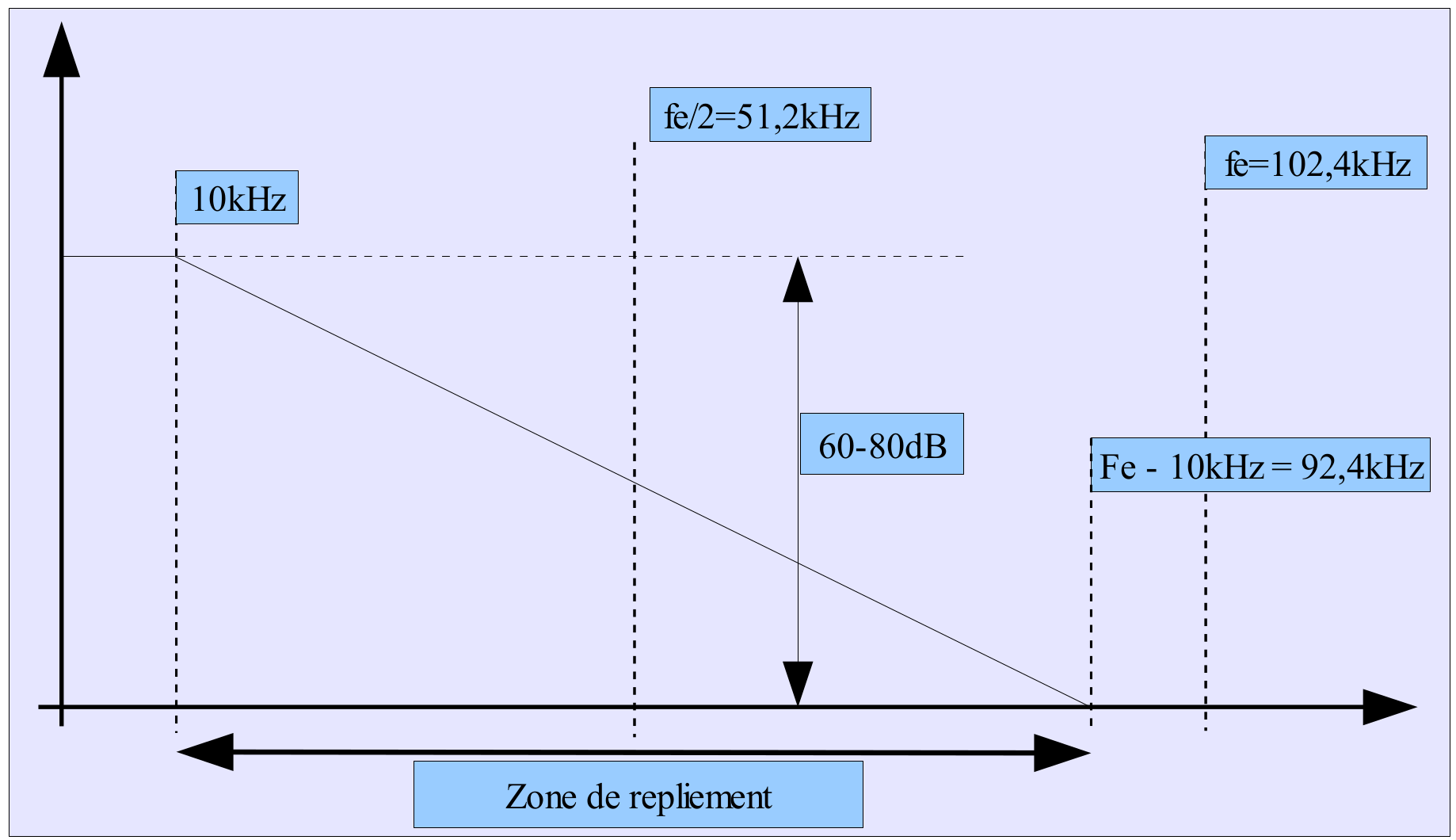

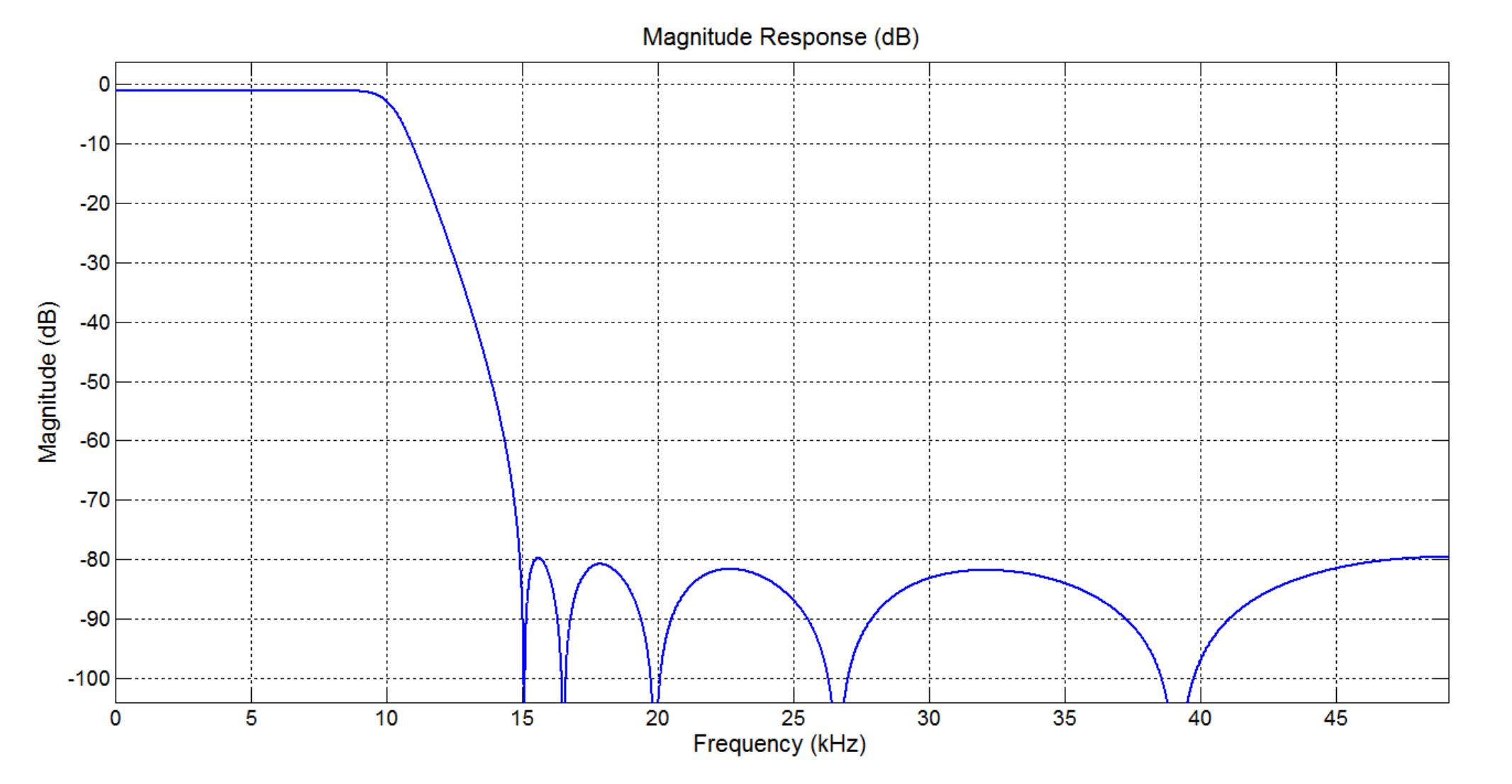

Ok, digital filter(s) but which one(s)?¶

- FIR -> too many operations and memory

- Multi-rate FIR -> still too many memory

- CIC -> benefits come at high decimation rate, sin(X)/X like TF

- IIR -> needs careful design

98 304Hz to 24 576Hz filter¶

- 5 stages Direct Form I

98 304Hz to 24 576Hz filter¶

RTL implementation flow, don't try to be smart¶

- Matlab or SciPy.signal

- Naive implementation C/C++/Python...

- Fixed point conversion/optimization

- RTL implementation with tests

observations:

- impulse response is easy to compute...

- one can read/write files from VHDL simulation...

Offset bug¶

Sometime LFR starts with a random offset or an oscillation on some channels

- reproduce on instrument

- investigate

- reproduce on simulation

- implement non regression test

- fix the bug

- buy new FPGAs :(

Offset bug¶

- When initialized with random content a fixed point recursive filter may start in an "unstable" state

- Doesn't affect floating point implementation of recursive filters

- Always reset filters with 0!

Done with bugs?¶

ADC bug -20°C¶

ADC bug¶

Reminder, LFR SOC¶

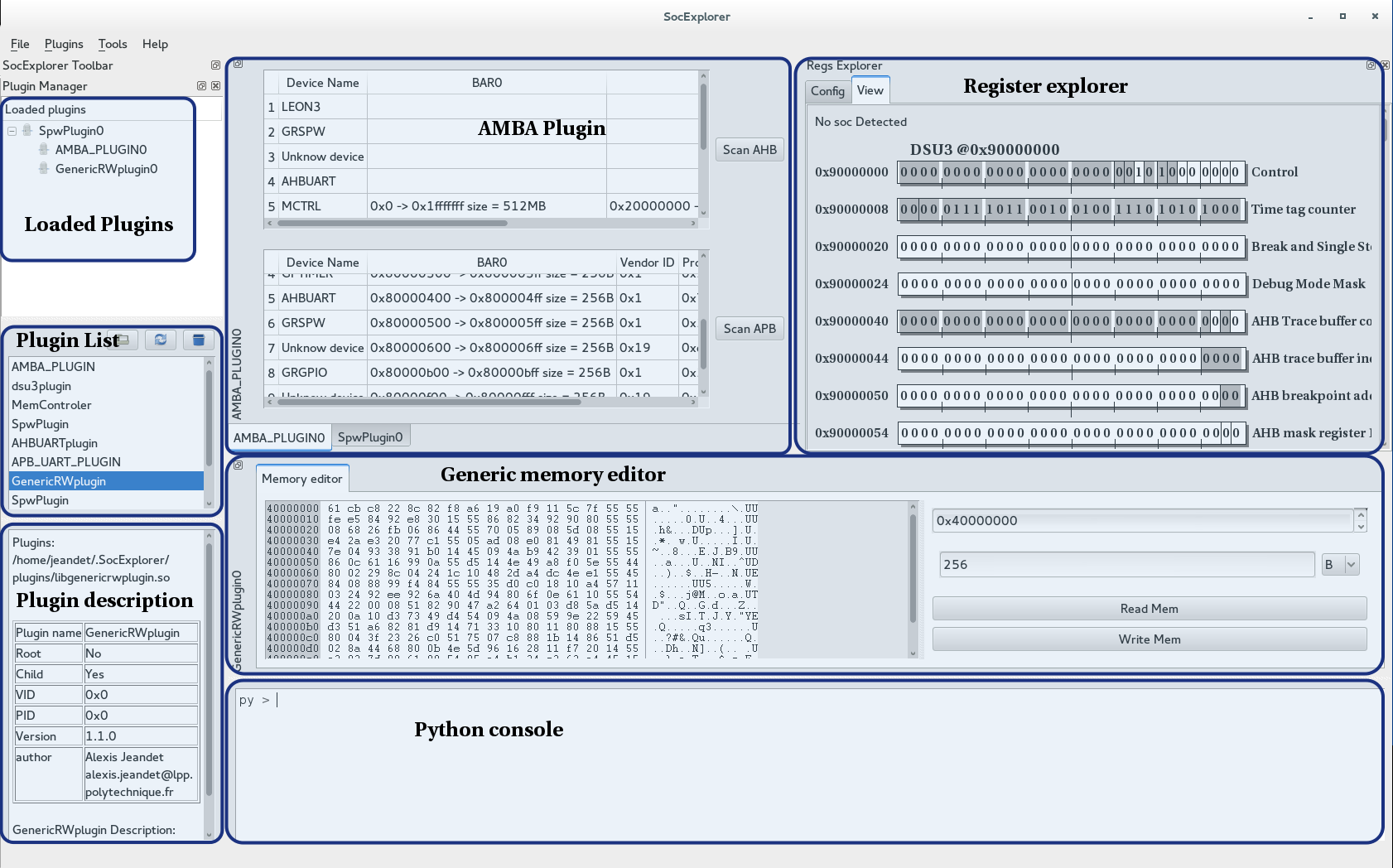

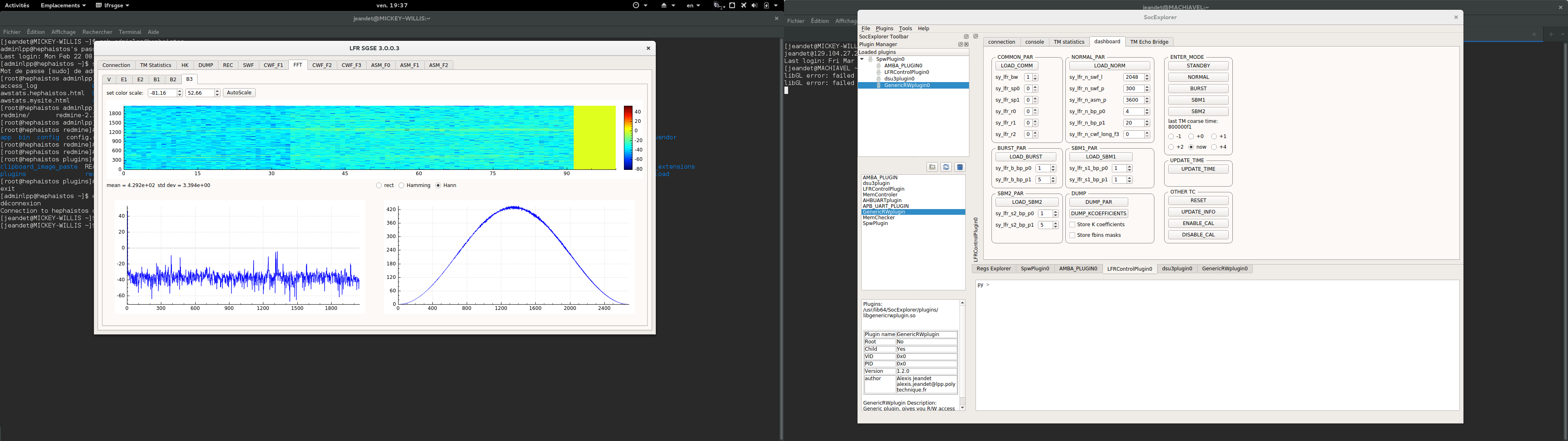

SocExplorer¶

a flexible framework to test them all¶

- Focuses on SOC control/exploration

- Allows from IP unit testing to system level performances measurements

- From manual registers investigation to automated head-less tests batch

- Gives a remote access to the whole SOC memory from your computer

- Heavily extensible with plugins

- Script with Python -> can virtually do anything with python

- Used for all LFR tests, from hardware to software

Lessons learned¶

- What is not tested doesn't work

- Tools are the key to success

- Prefer open source solutions to proprietary ones

What next?¶

- Both code and HW are open source!

- Next generation could rely on tinny CPU arrays -> ASIC? RISC-V?

- Onboard machine learning for event detection and classification

- A lot of reusable blocks for ground equipment

- Open source flexible testbench under development

- Analyzers knowledge used for next generation digital search-coils

Contributors:¶

- Thomas Chust

- Paul Leroy

- Martin Morlot

- Yannic Simon

- Clotilde Laigle

- Pedro Luiz Coelho Rodrigues

- Gerald Saule

- Jean-Christophe Pellion

- Bruno Katra

- Veronique Bouzid